Eclipse基金会推出企业级开源替代方案,取代微软的VS Code市场

The New Stack

·

Yelp正在大幅提升其AI聊天助手的实用性

The Verge

·

在Omacon庆祝计算机

David Heinemeier Hansson

·

DEKRA德凯2025年营收同比增长3.4%达44亿欧元

全球TMT-美通国际

·

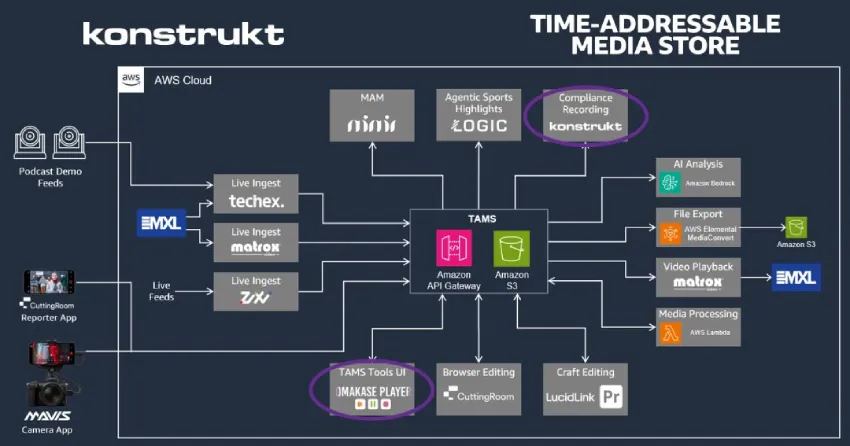

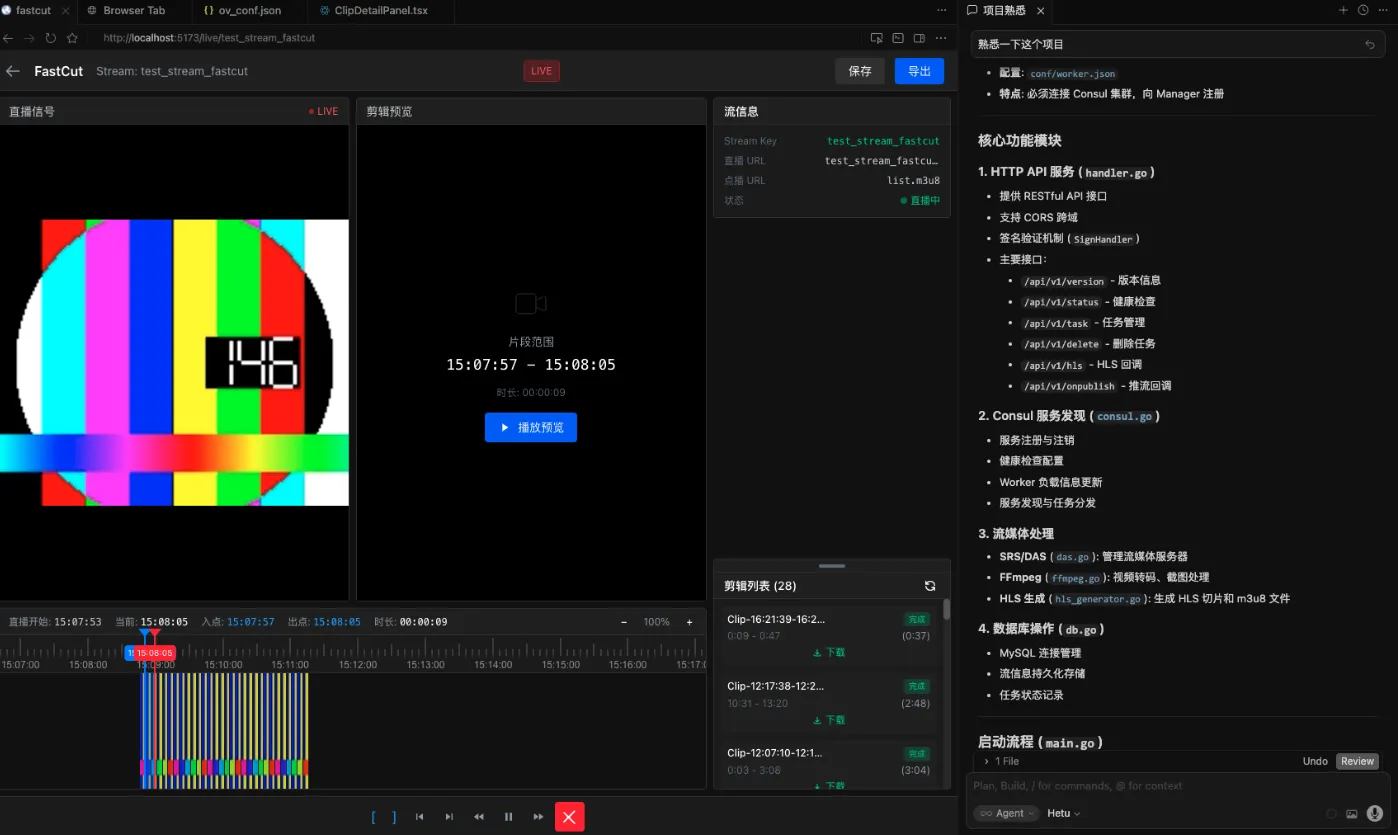

从零构建在线直播编辑分布式系统:架构设计与实现

实时互动网

·

Dematic与GreyOrange合作,进一步拓展柔性自动化能力

全球TMT-美通国际

·

海信推出新一代旗舰产品,全面提升球迷世界杯观赛体验

全球TMT-美通国际

·

Antony Pegg:如何使用 pgEdge 控制平面:从零到多主及更远

Planet PostgreSQL

·