💡

原文中文,约10900字,阅读约需26分钟。

📝

内容提要

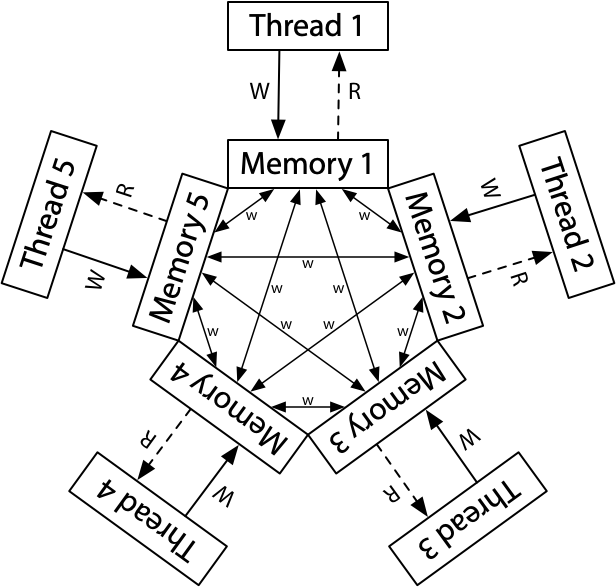

本文探讨了硬件内存模型对多线程程序的影响。随着多核处理器的普及,程序员需理解内存一致性问题及硬件和编译器优化对程序行为的影响。顺序一致性是理想模型,但现代硬件常偏离此模型,导致程序在不同平台上表现不一致。文章还讨论了通过内存屏障等手段确保程序正确性的方法。

🎯

关键要点

- 本文探讨了硬件内存模型对多线程程序的影响。

- 程序员需理解内存一致性问题及硬件和编译器优化对程序行为的影响。

- 顺序一致性是理想模型,但现代硬件常偏离此模型,导致程序在不同平台上表现不一致。

- 内存一致性模型是硬件和编译器对程序员的承诺。

- 早期内存模型只关注硬件对汇编程序员的承诺,编译器不在考虑范围内。

- 顺序一致性模型要求所有处理器的操作按某种顺序串行执行。

- litmus测试用于确定特定程序执行结果的可能性。

- 现代x86系统的内存模型采用总存储顺序(TSO),允许写入排队。

- ARM和POWER系统的内存模型比x86-TSO更弱,允许更大的重新排序。

- 内存屏障可用于控制内存操作的顺序,确保程序的正确性。

- 弱排序和无数据竞争的顺序一致性为程序员提供了简化的编程模型。

- DRF-SC模型为硬件设计者和软件作者提供了清晰的策略。

➡️